## 一种小波分解滤波器高速实现结构 1

#### 尚勇\*\*\* 罗丰\*\* 吴顺君\*\*

\*(北京大学电子学系 北京 100871)

\*\*(西安电子科技大学雷达信号处理重点实验室 西安 710071)

摘 要 近年来,小波变换得到了广泛的应用,快速塔式分解算法是它应用的一个有利工具,其地位相当于 FFT 之于 Fourier 分析,因此 DWT 的快速硬件实现变成了其应用的一个重要问题,本文通过将并行 systolic FIR 滤波器结构引入小波分解滤波器的设计,得到了一种小波分解滤波器的实现结构。该结构由于 应用了 systolic 技术及采用并行结构,除了可以提高运算速度外,还可以提高系统的数据吞吐率以及降低系统功耗

关键词 小波分解, Systolic 结构, 并行实现

中图号 TN713, O177.6

#### 1引 言

小波分析和它在信号处理领域中的应用是一个正在迅速发展的学科,目前,其重要的数学基础和理论框架已经建立 [1] . 小波分析具有较好的时域和频域局部化特性,被广泛地应用在许多信号处理领域。特别是 80 年代后期, Mallat 塔式分解算法是小波步入应用的一个重要里程碑,其地位相当于 FFT 在 Fourier 分析中的作用。目前的实现多基于软件编程,硬件实现的研究相对落后,本文通过将并行 systolic FIR 滤波器结构应用于小波滤波器结构的设计,得到一种适合于 VLSI 实现的小波滤波器结构。在这种结构中,可同时完成塔式分解中的 FIR 滤波和下 2 采样或小波重构中的 FIR 滤波和上 2 采样。若进一步采用数据序列重新排序策略,则可用同一组滤波器完成多级分解或重构。

## 2 离散小波分解的快速算法

小波分解的理论和应用研究已十分成熟, Mallat 快速算法是其广泛应用的算法基础。本文主要从快速算法的核心运算—— FIR 滤波和上 2、下 2 采样的具体实现角度给出一种高效的 systolic 实现结构。为了后面讨论问题方便,在这里有必要对离散小波分解的快速算法—— Mallet 塔式算法做一简要回顾。

设  $\{\varphi,\psi,\tilde{\varphi},\tilde{\psi}\}$  是一个双正交小波系统,满足双尺度方程:

$$\varphi(x) = \sum_{k} h(k)\varphi(2x - k)

\psi(x) = \sum_{k} g(k)\varphi(2x - k)

\uparrow \Pi

\tilde{\psi}(x) = \sum_{k} \tilde{g}(k)\tilde{\varphi}(2x - k)

\uparrow \Pi

\tilde{\psi}(x) = \sum_{k} \tilde{g}(k)\tilde{\varphi}(2x - k)$$

(1)

其中  $\varphi$ ,  $\psi$  为尺度函数和小波函数,  $\tilde{\varphi}$ ,  $\tilde{\psi}$  为对偶尺度函数和对偶小波函数。而  $\{h,g,\tilde{h},\tilde{g}\}$  为相应的双正交滤波器组。

设已经得到了第 J 层的逼近系数  $c_J(l)$ ,  $l \in Z$ ,根据双尺度变换关系,可以得到后续各层的逼近系数和细节系数,即当 j < J 时,有

<sup>1 1999-09-29</sup> 收到, 2000-01-05 定稿

$$c_{j}(l) = \frac{1}{\sqrt{2}} \sum_{k} c_{j+1}(k) \tilde{h}(k-2l)$$

(2)

$$d_{j}(l) = \frac{1}{\sqrt{2}} \sum_{k} c_{j+1}(k) \tilde{g}(k-2l)$$

(3)

根据双尺度变换可得重构公式如下 (当 j < J 时):

$$c_{j+1}(l) = \frac{1}{\sqrt{2}} \left[ \sum_{k} c_j(k) h(l-2k) + \sum_{k} d_j(k) g(l-2k) \right]$$

(4)

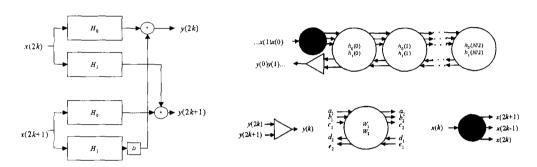

(4) 式即是著名的 Mallat 塔式算法。图 1 给出了双正交小波分解的实现框图 (图中忽略了常数 项  $1/\sqrt{2}$ )。

图中 h, g,  $\tilde{h}$ ,  $\tilde{g}$  均可用 FIR 滤波器实现。对于 Mallat 塔式算法,一个重要的问题是初始化问题。如果初始信号是连续时间信号,首先应获得最细的一层逼近系数,它的获得可采用预滤波或特殊的小波类型,如内插小波等。若信号本身是离散信号,可直接用此离散信号做初始逼近系数。通过初始逼近系数和 Mallat 算法可快速计算粗分辨逼近系数和细节系数。

针对图 1 中 FIR 滤波器的具体实现,我们提出了一种并行的 systolic 结构。这种结构适用于双正交 FIR 的小波系统和正交小波系统。

## 3 FIR 滤波器并行 systolic 实现

下面首先介绍一种 FIR 滤波器的并行实现结构。由文献 [2,3] 可得下式所示的 FIR 滤波器并行结构:

$$\sum_{i=0}^{L-1} Y_i(z^L) z^{-1} = \sum_{j=0}^{L-1} H_j(z^L) z^{-j} \sum_{l=0}^{L-1} X_l(z^L) z^{-1}$$

(5)

由 (5) 式可见: 对一个 N 阶 FIR 滤波器而言,可用  $L^2$  个长度均为 N/L 的 FIR 滤波器实现。 下面以 2 输入 2 输出的情况 (L=2) 为例介绍 FIR 滤波器的并行实现结构:由 (5) 式可得

$$Y = Y_0 + z^{-1}Y_1 = (X_0 + z^{-1}X_1)(H_0 + z^{-1}H_1)$$

=  $(X_0H_0 + z^{-2}X_1H_1) + z^{-1}(X_0H_1 + X_1H_0)$  (6)

图 2 示出 (6) 式所表示的并行结构。 D 为单位时延。输入序列分为奇、偶序列,分别从两输入支路输入,输出也分为奇、偶两路。

很显然,并行 FIR 滤波器提高了数据的吞吐率 (如果时钟频率一样,它比串行滤波器提高 L 倍;即并行滤波在速度上比串行滤波快 L 倍,这里 L 的含义已在上面给出)。除此之外,并行处理还有另一个重要优点是可减小 FIR 滤波器的功耗。

在文献 [4] 中,我们结合前面对并行 FIR 滤波器结构的分析,以一般 FIR 滤波器 systolic 结构 [5] 为基础提出了一种 systolic 结构, 本文提出的实现结构, 对其进行了改进, 改进结构

更加适用于塔式算法,将其应用于多分辨分析,效率更高.为了后面讨论方便,这里首先给出文献[4]中的结构(见图 3),并予以简单说明:

对图 3 有如下假定,图中每个节点内的运算都在"零时间"内完成,而各传输线上均应有一个延时 D ,为了画图清晰,图中没有将其标出。

图 2 2 输入 2 输出并行 FIR 滤波器结构

图 3 一种实现并行 FIR 滤波的 systolic 结构

下面给出图中各处理单元的功能。

空心圆单元有5个输入和5个输出、功能定义如下:

$a_2=a_1;\ b_2=b_1;\ c_2=c_1;\ d_2=b_1\times W_2+c_1\times W_1+d_1;\ e_2=a_1\times W_1+c_1\times W_2+e_1$ . 该处理单元主要用于实现乘和累加运算,是完成 FIR 滤波的主要运算部件。最左边的空心圆的  $d_2$  和  $e_2$  分别对应图 2 中的输出 y(2k) 和 y(2k+1)。 实心圆单元功能和三角单元功能的定义已标在图中。其中:实心圆将输入信号分为偶、奇以及延迟的奇三个序列,分别代表图 2 中的 x(2k) , x(2k+1) 以及延迟一步的 x(2k-1) 。三角单元将奇、偶输出 y(2k+1) , y(2k) 合并为一路输出 y(k) 。这两种处理单元的实现均较为简单。

文献 [4] 中对上面的并行 FIR 滤波的 Systolic 结构和一般的 FIR 滤波的 systolic 结构进行了比较,由比较结果可见采用并行结构比采用一般 FIR 滤波的 systolic 结构具有一定的优越性.

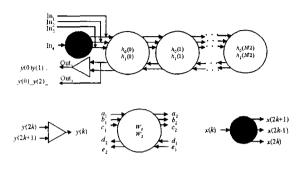

如果将图 3 的 systolic 结构用于本文上面提到的塔式算法中,最直接的方法是将图 1 中的 h, g,  $\tilde{h}$ ,  $\tilde{g}$  分别用图 3 的结构实现。这种实现方案思想清楚,但实现效率却不是最高的。下面我们给出一种高效的实现方案。这种方案比第一种方案具有更高的效率和更简单的结构。通过分析可以发现,在塔式算法中,信号分解后和重构前,分别要进行下 2 和上 2 采样,而 2 输入 2 输出并行 FIR 滤波器结构本身就具有将输入输出信号按奇偶支路采样的功能,如果利用其结构的这一特点,通过对图 3 结构做适当改动,就可得到一种可同时完成下 2 和上 2 采样和 FIR 滤波的并行 systolic 结构。图 4 给出了这一结构。图中,各功能单元的定义与图 3 中的相同。这里需补充说明的一点是:图 4 结构可以工作在三种模式下,

模式 1 输入信号接  $In_4$ , 而  $In_1$ ,  $In_2$ ,  $In_3$  分别处于高阻状态;输出信号接  $Out_2$ ,  $Out_1$  处于高阻状态.

模式 2 输入信号接  $In_1$ , 而  $In_2$ ,  $In_3$  接地输入 '0',  $In_4$  处于高阻状态;输出信号接  $Out_1$ ,  $Out_2$  处于高阻状态.

模式 3 输入信号接  $In_4$  , 而  $In_1$  ,  $In_2$  ,  $In_3$  分别处于高阻状态;输出信号接  $Out_1$  ,  $Out_2$  处于高阻状态.

图 4 改进的并行 FIR 滤波的 systolic 结构

将图 4 结构应用于塔式算法时,对应于图 1 结构,在进行多分辨分解时,FIR 滤波器工作在模式 1 状态,而在进行信号重构时,FIR 滤波器工作于模式 2. 值得注意的是,此时,由于该结构同时实现了滤波和上 2 或下 2 采样,故在塔式分解和重构实现框图中,不需再进行上 2、下 2 采样。在有些应用场合,无需对分解信号进行重构,此时的一种比较有效的分解结构

无需下 2 采样, 而图 4 结构工作于模式 3, 恰好能满足这种滤波器结构的要求.

对于图 1 结构中的 h, g,  $\tilde{h}$ ,  $\tilde{g}$  均可用图 4 的 systolic 结构实现,由于塔式算法中各级分解和重构所采用的 h/g,  $\tilde{h}/\tilde{g}$  均相同,故通过输入数据重新排序,可只使用其中的一对滤波器来完成多级滤波。对于分解滤波器,即当  $c_j$  数据计算完成后,将保存在 ROM 中的  $c_{j+1}$  返回输入端进行第 2 轮计算,依次类推,直至最终可得小波分解结果。当然这种简化系统设计的方法是以降低整个系统的运行速度和增加系统存储容量为代价的。但通过下面的分析可以看到,这种折中是有实际意义的。

考虑到增加滤波器的个数就意味着增加整个系统中乘法器和加法器的个数,而这一数量的增加是成倍的,例如滤波器长度为 N=6,进行 M=4 级的小波分解,如果用多个滤波器实现,则需 2NM=48 个乘法器和 2(N-1)M=40 个加法器。当采用一对滤波器完成滤波时,所需乘法器和加法器的个数分别为 12 和 10 . 而我们知道,在 VLSI 技术中,实现乘法的代价相对较大,乘法器数量的增加有可能使得芯片规模过大而难以实现。故在实际实现中,有必要通过折中考虑来换取系统的可实现性。而本文中给出的并行 systolic 结构,与实现 FIR 滤波的一般结构相比,具有更高的系统输入输出速率。这正好能部分抵消因采用上面数据重排方案而引起的系统运行速度减慢。从而得到一种既易于实现又有较高系统速率的滤波器结构。

根据割集重定时序方案  $^{[6]}$  和前面介绍的多项式分解的有关知识可知,对图  $^{2}$  信号流图,若按  $D \sim KD'$  进行时间标度,结合  $^{2}$  (5) 式给出的并行 FIR 滤波器结构 (此时取 K=L),就可得到用大约 K 分之一的处理单元数来实现滤波的 FIR 滤波器 systolic 结构。当然,此时各处理单元的功能复杂程度也会随着 K 的增加而增加。对于 K 的选取可视具体情况而定。此时同样可以将其设定为三种工作模式,可直接用于 M(M=K) 带小波滤波系统。

## 4 结 论

本文通过把 FIR 滤波器并行实现引入 FIR 滤波器 systolic 结构的设计,得到了一种新的 FIR 滤波器 systolic 结构. 当这种结构工作于不同模式时,可满足不同小波滤波器 (包括分解、重构和非下 2 采样等滤波器) 的滤波要求. 与一般的 FIR 滤波器 systolic 结构相比,该结构具有阵列规模小;系统功耗低;能适应更高处理速度的优点. 本文将这种结构应用于小波分解的 塔式快速算法,得到了较为满意的结果.

**致谢** 在本文的写作过程中,得到了水鹏朗博士的大力帮助。水博士从概念分析到文章结构都给予了很好的建议。在此对水鹏朗博士表示感谢!

#### 参考文献

- [1] 水鹏朗,广义内插小波和递归内插小波理论及应用的研究,[博士论文], 西安, 西安电子科技大学, 1998.

- [2] Shang Yong, Wu Shunjun, Design of parallel adaptive FIR filters, IEEE APCCAS'98, Chiangmai, Thailand, 1998, 81-84.

- [3] P. P. Vaidyanathan, Multirate digital filters, filter banks, polyphase networks, and applications, A tutorial. Proc. IEEE, 1990, 78(1), 56-93.

- [4] 尚勇, 吴顺君, 一种新的 FIR 滤波器脉动实现结构, 电子学报已录用.

- [5] 贡三元, VLSI 阵列处理, 南京, 东南大学出版社, 1992, 132-193.

- [6] S. K. Rao, T. Kailath, Regular iterative algorithms and their implementation on processor arrays. Proc. IEEE, 1988, 76(3), 259-269.

# AN IMPLEMENTATION OF WAVELET DECOMPOSITION FILTER BASED ON SYSTOLIC STRUCTURE

Shang Yong\* \*\* Luo Feng\*\* Wu Shunjun\*\*

\*(Department of Electronics, Peking University, Beijing 100871, China)

\*\*(Key Lab for Radar Signal Processing, Xidian University, Xi'an 710071, China)

Abstract In recent years, the wavelet transform has been widely used in many fields. The fast tower-type algorithm is an efficient tool. Its importance is just like that of FFT in the Fourier analysis. Therefore the hardware implementation of the DWT is an important problem in its applications. With the introduction of the parallel systolic FIR filter structure to the design of the wavelet decomposition filter, an implementation structure of wavelet decomposition filter is presented in this paper. As being parallel and systolic, the structure can increase data throughput and reduce power consumption of the system as well as enhance operation speed.

**Key words** Wavelet decomposition, Systolic structure, Parallel implementation

- 尚 勇: 男,1970年生,博士后,研究兴趣及方向: 自适应信号处理,并行信号处理,阵列信号处理等:

- 罗 丰, 男,1971 年生,讲师,研究兴趣及方向。专用芯片研究及设计,可编程逻辑器件设计及实现,小波信号处理等.

- 吴顺君: 男, 1942 年出生,教授,博士生导师,中国电子学会会士,西安电子科技大学雷达信号处理国家重点实验室主任,长期从事信号和信息处理方面的教学和科研工作.