## 三值电路和电路三要素理论 1

#### 方振贤 刘 莹

(黑龙江大学信息与电子科学系 哈尔滨 150080)

摘 要 本文基于四值代数,提出三值电路的统一理论——电路三要素 (信号, 网络和负载) 理论, 该理论表明: 门级与开关级电路间, 开关级电路结构间, 动态与静态电路间存在简单的转换关系, 依照这个关系很容易由三值函数式设计出三值电路, 尤其能基于一个电路方程同时推出三值动态和静态电路。

关键词 电路三要素,四值代数,动态和静态电路中图号 TN79

### 1 四值代数和三值开关量

三值数字电路目前研究十分广泛,其中开关-信号理论较突出<sup>[1]</sup>。本文进一步提出信号、网络和负载的电路三要素理论。实际上,二值电路为克服开关理论的不足,已应用了电路三要素理论<sup>[2,3]</sup>。为了推广到三值电路,首先提出四值代数,作为三值电路的研究工具。

定义 1 《  $H, +, \bullet, -, \uparrow, \Rightarrow, 0, *, 1, 2$  》为具有五个基本运算和四个定元的四值代数,满足:  $\forall x, y \in H, (1) \ x + y = \max(x, y), \ x \cdot y = \min(x, y), \ 0 < * < 1 < 2, (2) \ x \uparrow y = {}_x y = {}_x$   $\underbrace{\exists x = *}_{y, \exists y \neq *}, (3) \ \overline{x} = {}_x \underbrace{\exists x = *}_{2-x, \exists x \neq *}, \ \text{又当} \ x = 0, *, 1, 2 \ \text{时}, \quad \overrightarrow{x} = *, 1, 2, 0 \ .$

定理 1 (1)  $\overline{A} = \overline{A}$ . (2) 若  $AB \neq *1$  和 1\*, 则 AB = AB, AB = AB, AB = AB, AB = AB, AB = AB.

证明 用真值表推出。

证毕

"与"和"或"运算满足交换律,结合律,分配律和吸收律[1,2]。记  $F_{\delta i} = \begin{cases} 2, & \exists F = i, \\ 0 & \exists F \neq i \end{cases}$

显然, $F_{\delta 1} = {}_0(F\overline{F})$ ,由 ⇒ 得出其余  $F_{\delta i}$  . 用它得出四值函数一维展开定理: $F(A,B,\cdots,Z) = \sum_{i \in B_4} A_{\delta i} F(i,B,\cdots,Z)$ , $B_4 = \{0,*,1,2\}$  . 指数运算↑是理论的关键,当 F = \* 时, $_x F = x$ ,表示开关 F 接通,输出为 x; 反之,  $F \neq *$  时,表示开关断开,输出取决于负载或假想负载,仅取 0,1 和 2 之一,记为  $\epsilon$ ,即输出为  $\epsilon$  . 按一维展开定理对 F 展开,参照文献 [2] ,令  $F = < f_\epsilon >$ ,得出开关量表示如下:

$$F = \langle f_{\delta} \rangle = *f_{\delta} + \epsilon \overline{f}_{\delta}, \quad f_{\delta} \in B_2 = \{0, 2\}. \tag{1}$$

控制信号  $f_{\delta}$  是二值布尔函数,有两基本形式:  $f_{\delta} = a_{\delta}b_{\delta}$ ,  $f_{\delta} = a_{\delta} + b_{\delta}$ , 代入 (1) 式,引伸出串联和并联运算  $\uparrow$  和  $\parallel$  如下 (运算的优先次序为  $\uparrow$ , $\parallel$ , $\bullet$ ,+)。

$$\langle a_{\delta} \cdot b_{\delta} \rangle = * \cdot a_{\delta} b_{\delta} + \epsilon \cdot \overline{a_{\delta} b_{\delta}} = \langle a_{\delta} \rangle \uparrow \langle b_{\delta} \rangle,$$

(2a)

$$\langle a_{\delta} + b_{\delta} \rangle = * \cdot a_{\delta} + b_{\delta} + \epsilon \cdot \overline{a_{\delta} + b_{\delta}} = \langle a_{\delta} \rangle || \langle b_{\delta} \rangle,$$

(2b)

$$\langle 2 \rangle = *, \quad \langle 0 \rangle = \epsilon. \tag{2c}$$

<sup>&</sup>lt;sup>1</sup> 1997-06-05 收到, 1998-09-12 定稿 黑龙江省自然科学基金资助项目

定理 2  $< F(a_{\delta}, \overline{a}_{\delta}, b_{\delta}, \overline{b}_{\delta}, \cdots, +, \bullet, 2, 0) >= F(< a_{\delta} >, < \overline{a}_{\delta} >, < b_{\delta} >, < \overline{b}_{\delta} >, \cdots, \parallel, \uparrow, \star, \epsilon)$ .

证明 由 (2) 式得出二代数系统《 $S,+,\bullet,2,0$ 》和《 $R,\parallel,\uparrow,*,\epsilon$ 》同构, 设 S 中有  $< y_{\delta} >= F(< a_{\delta} >, < \overline{a_{\delta}} >, < b_{\delta} >, < \overline{b_{\delta}} >, \cdots, \parallel,\uparrow,*,\epsilon)$ ,对应 R 中有  $y_{\delta} = F(a_{\delta}, \overline{a_{\delta}}, b_{\delta}, \overline{b_{\delta}}, \cdots, +, \bullet, 2, 0)$ ,将  $y_{\delta}$  代入上式,即得该定理。 证毕

定义 2  $x_1 < f_{1\delta} > |x_2| < f_{2\delta} > \cdots |x_k| < f_{k\delta} > = |x_i| < f_{i\delta} > = \sum_{i \in K} x_i f_{i\delta} + \epsilon \sum_{i \in K} f_{i\delta}, \forall i, j \in K, x_i \neq x_j \Rightarrow f_i f_j = 0$ .

定义 3(网络转换定理)  $\prod_{i \in K} x_i f_i(\langle a_\delta \rangle, \langle b_\delta \rangle, \cdots, ||, \uparrow, *, \epsilon) = \sum_{i \in K} x_i f_i(a_\delta, b_\delta, \cdots, +, \epsilon)$

$\bullet, 2, 0) + \epsilon \sum_{i \in K} f_i(a_\delta, b_\delta, \dots, +, \bullet, 2, 0), \forall i, j \in K, \stackrel{\overset{\cdot}{\leftarrow}}{\leftarrow} x_i \neq x_j, \quad \emptyset \quad f_i f_j = 0.$

证明 由定义2和定理2直接得出。

证毕

源信号加载:记  $x \uparrow R < a_{\delta} >= x < a_{\delta} >^R$  为源信号加载 (串接 R),其作用由广义约束条件 (3) 式描述,其中 (3a) 式描述电阻分压形成 1 电平; (3b) 式描述导通开关钳位作用, $\sum_{i \in k}^d a_{i\delta}$  视为  $b_{j\delta}$  的冗余项。

$$1 < b_{i\delta} >^{R} = _{0} < b_{i\delta} >^{R} \mid _{2} < b_{i\delta} >^{R},$$

$$\downarrow_{i \in K} x_{i} < a_{i\delta} > \underset{j \in K_{1}}{\downarrow} x_{j} < b_{j\delta} > = \underset{i \in K}{\downarrow} x_{i} < a_{i\delta} > \underset{j \in K_{1}}{\downarrow} x_{j} < b_{j\delta} >^{R}$$

$$= \underset{i \in K}{\downarrow} x_{i} < a_{i\delta} > \underset{j \in K_{1}}{\downarrow} x_{j} \left\langle b_{j\delta} + \sum_{i \in K}^{d} a_{i\delta} \right\rangle^{R},$$

$$\forall i, j \in K, x_{i} \neq x_{j}, f_{i}f_{j} = 0, K \cap K_{1} = \Phi.$$

$$(3a)$$

### 2 三值电路统一性和三值电路

统一性表现在: (1) 门级与开关级电路间纵向关系。(2) 各开关级结构间横向关系。(3) 动态和静态电路间侧向关系。(4) 二值和三值电路间的层间关系。实现统一性的关键是体现电路三要素: 信号, 网络和负载, 而不是逻辑关系。本文重点考虑(1) 和(3)。

定理 4

$$\prod_{i \in K} a_i (< a_{i\delta} > \uparrow < b_{\delta} >) = (\prod_{i \in K} a_i < a_{i\delta} >) \uparrow < b_{\delta} >= a_i < b_{\delta} >,$$

其中

$$x = \bigcup_{i \in K} x_i < a_{i\delta} > = \sum_{i \in K} x_i a_{i\delta} + \epsilon \overline{\sum_{i \in K} a_{i\delta}}, \forall i, j \in K, 若 x_i \neq x_j, 则 a_i a_j = 0$$

.

可控开关有二种表示型: (1) $\delta$  型, 即  $F = \langle f_{\delta} \rangle$ ,  $f_{\delta}$  为导通条件 ( $\langle f_{\delta} \rangle = *$  或  $f_{\delta} = 2$  时导通),对三值信号  $f \in B_3 = \{0,1,2\}$ ,若仅当 f = i 时导通,则  $f_{\delta} = f_{\delta i}$ ;若仅当 f = i, 时导通,则  $f_{\delta} = f_{\delta i}$ ;者仅当 f = i, 时导通,则  $f_{\delta} = f_{\delta i} + f_{\delta j} = f_{\delta i j}$ ,余类推。 (2) 域值型,记为  $F = \langle t f \rangle$ , $t > 0^{[3]}$ ,当 f > t 时开关导通。若  $f = \overline{a}$ ,则  $F = \langle t \overline{a} \rangle = \langle t \overline{a} \rangle$ ,前者输入为  $\overline{a}$ ,  $\overline{a} > t$  时导通,  $t = |V_{TP}|$ ,因为  $\overline{a} > t$ ,即 2 - a < t,所以 a < 2 - t 。控制信号有下列关系:

$$f_{\delta i} = \overline{f}_{\delta \overline{i}}, \quad f_{\delta ij} = \overline{f}_{\delta \overline{i} \ \overline{j}}, \quad {}^{t}\overline{a} = {}^{t} \stackrel{\cdots}{a},$$

(4a)

$$f_{\delta 1,2} = {}^{0.5}f, \quad f_{\delta 2} = {}^{1.5}f, \quad f_{\delta 0,1} = {}^{0.5}\overline{f} = {}^{0.5}\overline{f}, \quad f_{\delta 0} = {}^{1.5}\overline{f} = {}^{1.5}\overline{f}.$$

(4b)

对二值信号  $\varphi \in B_2 = \{0,2\}$  ,可略去 t 不记,即  ${}^t\varphi = \varphi$  ,  ${}^t\overline{\varphi} = \overline{\varphi} = {}^t\overline{\varphi}$  . 任意不完全描述三值函数 y 在 n 维卡图中按 i(=0,1,2 和  $\epsilon)$  方格划环得  $f_i$  ,于是变换 y 为开关网络式如下:

$$y = 0 \cdot f_0 + 1 \cdot f_1 + 2 \cdot f_2 + \epsilon \overline{f_0 + f_1 + f_2}$$

$$\frac{\cancel{\text{E}}\cancel{\text{E}}\cancel{\text{B}}}{0} < f_0 > |_{1} < f_1 > |_{2} < f_2 > = 0 < f_0 > |_{1} < f_1 >^{R} |_{2} < f_2 >$$

$$\frac{(3a) \cancel{\text{E}}}{0} < f_0 > ||_{1} < f_1 >^{R} |_{2} < f_2 > ||_{1} < f_1 >^{R}$$

$$= 0 (< f_0 > ||_{1} < f_1 >)^{R} |_{2} (< f_2 > ||_{1} < f_1 >)^{R} (\text{cmos}).$$

(5)

不完全描述相应真开路  $\epsilon = \bar{\epsilon}$ (即空载,可略去标记  $\epsilon = \bar{\epsilon}$  不写),此时输出不确定,也即输出随假想负载而变。若降维为 r 维卡图 (r < n),按同符号方格划环,可得出传输门型三值电路。源信号有直流  $(+V_{DD}, +V_{DD}/2$  或地)和交流  $(\text{如 }x_i)$  两种选取方式,各自相应于选取 n 维卡图和 r 维卡图 (代数方法相应为按 n 维展开和按 r 维展开)。完全描述三值函数满足:

$$f_0 + f_1 + f_2 = 2, \quad f_0 + f_1 = \overline{f}_2, \quad f_1 + f_2 = \overline{f}_0,$$

(6a)

$$a_{\delta 01} = \overline{a_{\delta}}\overline{2}, \quad a_{\delta 12} = \overline{a_{\delta}}\overline{0}, \quad a_{\delta 012} = 2.$$

(6b)

利用 (6) 式可变换 (5) 式为完全描述三值函数开关网络式如下:

$$y = \frac{(5) \pm 1}{2} (1 + 1)^R + 1 = (1 + 1)^R + 1 = (1 + 1)^R$$

$\underline{\underline{\mathtt{c}}\,\underline{\mathtt{u}}\,\underline{\mathtt{2}}}_{\,\,0} < f_{0} > \| \ < f_{1} >^{R} \ \big| \ {_{2}} < f_{1} + f_{2} >^{R} = {_{0}} < f_{0} > \| < f_{0} + f_{1} >^{R} \ \big| \ {_{2}} < f_{0} + f_{1} + f_{2} >^{R}$

$$\stackrel{(6)}{=\!\!\!=\!\!\!=} _0 < \overline{f}_2 >^R \mid_{2} < \overline{f}_0 >^R (\operatorname{cmos}) \stackrel{(5)}{=\!\!\!=} _0 < f_0 > \mid_{2} < f_2 > \mid_{\epsilon=1},$$

(7)

其中  $\epsilon=2$  表示开路 2 电平负载,即串联 R 后再接  $+V_{DD}$ ; 类似  $\epsilon=0$  表示开路 0 电平负载,即串联 R 后再接地,而且  $<f_0+f_1+f_2>=<2>$  为常通开关。源信号 0 和 2 各表示接地和接  $+V_{DD}$  . 任意三值电路都可以由它的函数式推出开关级结构 (先按  $\delta$  展开,变换,再利用 (5) 式和 (7) 式)。

"或非"门:

$$y_{1} = \overline{a + b} = 0 \cdot (a_{\delta2} + b_{\delta2}) + 2 \cdot (a_{\delta0}b_{\delta0}) + 1 \cdot (a_{\delta1} + \cdots)$$

$$\frac{(7) \pm 0}{10} = (a_{\delta2} + b_{\delta2}) + (a_{\delta0}b_{\delta0}) + (a_{\delta1} + b_{\delta1}) + (a_{\delta1} + b_{\delta12}) + (a_{\delta12} + b_{\delta12$$

四态门:

$$y_{\delta} = \overline{a} \ \overline{\varphi} + \epsilon \varphi \frac{$$

定理  $\frac{3}{a} < \overline{\varphi} > \underline{$ 定理  $\frac{4}{0} < \overline{\varphi} > \uparrow < 0.5 a > ^R \ | \ _2 < \overline{\varphi} > \uparrow < 0.5 \overset{\dots}{a} > ^R \ (cmos).$  (8c) "非"门:

$$\overline{a} = 0 \cdot a_{\delta 2} + 2 \cdot a_{\delta 0} + 1 \cdot a_{\delta 1} = {}_{0} < a_{\delta 12} >^{R} \mid {}_{2} < a_{\delta 01} >^{R} \frac{(7) \, \, \sharp}{a} \, {}_{0} < {}^{0.5}a >^{R} \mid {}_{2} < {}^{0.5} \, \overset{\dots}{a} >^{R} (\text{cmos}). \tag{8d}$$

域门:

$$a_{\delta 0} = 0 \cdot a_{\delta 12} + 2 \cdot a_{\delta 0} = 0 < a_{\delta 12} > |_{\epsilon=2} = 0 < 0.5$$

$a > |_{\epsilon=2}$  (nmos). (8e)

右移门:

$$\vec{a} = 0 \cdot a_{\delta 2} + 2 \cdot a_{\delta 1} + 1 \cdot a_{\delta 0} \xrightarrow{(7) \text{ th} \atop 0} (3a_{\delta 2} > || (3a_{\delta 0} < ||$$

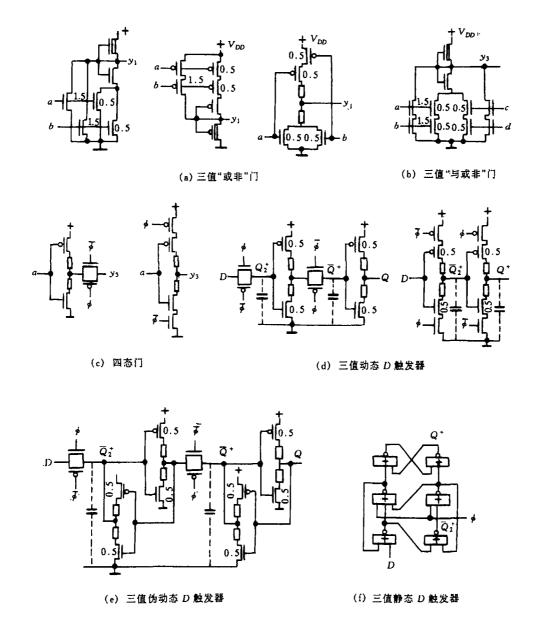

图 1 三值电路

根据 (8) 式画出电路图, 如图 1(a)-1(c) 所示。由此可见网络转换定理是定量描述门级与 开关级电路间纵向关系的基础。具有类似拉氏变换的作用。

# 3 三值动态时序电路和三值触发器

设三值网络  $\bigsqcup_{i \in L} z_i < S_{ik\delta} >$  接电容负载  $C_k$  ,参照二值电路理论  $^{[3]}$  ,由定理 3 得出

$$Q_k^+ = \prod_{i \in L} x_i < S_{ik\delta} > |_{\epsilon = Q_k} = \sum_{i \in L} x_i S_{ik\delta} + \epsilon R_k Q_k, \ k \in K, \ \forall i, j \in L, \ \nexists x_i \neq x_j, \ \emptyset S_{ik\delta} S_{j\delta} = 0,$$

其中  $L = \{1, 2, \dots, l\}$ ,  $R_k = \sum_{i \in L} S_{ki\delta}$  满足  $R_k \sum_{i \in L} S_{ik\delta} = 0$  和  $R_k + \sum_{i \in L} S_{ik\delta} = 1$  。设计电路时先画出状态表,继之求出状态方程,变换方程的形式,使之与上式形式一致,二者对照,得出  $R_k$  和  $\sum_{i \in L} x_i S_{ik\delta}$  ,并按上式写出元件级表达式。依据变换的结果可能有下列几种三值时序电路:

- (1) 所有  $R_k \neq 0$ ,且  $\sum_{i \in L} x_i S_{ik\delta}$  与  $Q_k$  无关,可实现三值动态时序电路;若部分  $R_k = 0$  或部分  $\sum_{i \in L} x_i S_{ik\delta}$  与  $Q_k$  有关,则得出三值混合动态时序电路。

- (2) 若所有  $R_k = 0$  , 必然  $\sum_{i \in L} x_i S_{ik\delta}$  与  $Q_k$  有关 (若无关, 则  $Q_k^+$  与  $Q_k$  无关,  $Q_k$  不是独立变量, 可删去) , 不用电容存储信息, 相应于三值静态时序电路。但若过渡态短时间 出现  $R_k = 2$ (竞争冒险) , 又称为三值伪动态时序电路。

由此将三值动态和静态时序电路的研究统一起来,它们是同一电路方程的不同电路实现。三值触发器的研究十分广泛,但迄今仅限于静态触发器 <sup>[4]</sup> ,尚未见三值动态触发器,以及三值动态和静态触发器的统一研究。三值 D 触发器满足下述电路方程 <sup>[5]</sup>

$$Q^{+} = Q\varphi + Q_{2}\overline{\varphi}, \quad Q_{2}^{+} = D\varphi + Q_{2}\overline{\varphi}. \tag{9}$$

利用网络转换定理既可将上述方程形式转换为电路形式,有可根据各型负载特性同时推出三值动态,伪动态和静态 D 触发器元件级电路结构。对动态电路取  $\epsilon = Q_k$  ,得出

$$Q^{+} = Q\varphi + Q_{2}\overline{\varphi} \stackrel{\underline{\underline{c}}\underline{\underline{q}}}{\underline{\underline{q}}} Q_{2} < \overline{\varphi} > |_{\epsilon = Q}$$

$$\stackrel{\underline{\underline{c}}\underline{\underline{q}}}{\underline{\underline{q}}} {}_{0} < \overline{\varphi} > \uparrow < {}^{0.5}\overline{Q}_{2} > {}^{R} \mid {}_{2} < \stackrel{\cdots}{\varphi} > \uparrow < {}^{0.5}\overline{\overline{Q}}_{2} > {}^{R} \mid {}_{\epsilon = Q},$$

$$\overline{Q}_{2}^{+} = \overline{D}\varphi + \overline{Q}_{2}\overline{\varphi} \stackrel{\underline{\underline{c}}\underline{\underline{q}}}{\underline{\underline{q}}} {}_{\overline{D}} < \varphi > |_{\epsilon = \overline{Q}}.$$

$$(10a)$$

$$\underline{\underline{\underline{\underline{r}}}} \stackrel{4}{\underline{\underline{q}}} {}_{0} < \varphi > \uparrow < {}^{0.5}D > {}^{R} \mid {}_{2} < \overline{\varphi} > \uparrow < {}^{0.5}\stackrel{\dots}{\underline{D}} > {}^{R} \mid {}_{\epsilon = \overline{Q}_{2}},$$

(10b)

$$\overline{Q}^+ = \overline{Q}\varphi + \overline{Q}_2\overline{\varphi} \ \underline{\underline{\widehat{c}}\underline{\pi}} \ \underline{\underline{3}}_{\overline{Q}_2} < \overline{\varphi} > |_{\epsilon = \overline{Q}},$$

$$Q_2^+ = D\varphi + Q_2\overline{\varphi} \stackrel{\underline{\text{cur } 3}}{\overline{D}} \langle \varphi \rangle |_{\epsilon = Q_2}. \tag{10c}$$

根据 (10a)–(10c) 式画出两种三值动态 D 触发器电路图,如图 1(d) 和图 1(f) 所示;图 1(d) 为传输门型,由 (10c) 式画出。也可按照门电路的方法,将  $Q_2$  和  $\overline{D}$  用代数法展开得出:  $\overline{D}=0\cdot D_{\delta 2}+2\cdot D_{\delta 0}+1\cdot D_{\delta 1}$ , $Q_2=0\cdot \overline{Q}_{2\delta 2}+2\cdot \overline{Q}_{2\delta 0}+1\cdot \overline{Q}_{2\delta 1}$ ,代入 (9) 式,推出的结果与上式相同。对于伪动态电路应选取  $R_k=\overline{\varphi+\overline{\varphi}}=0$ 。选取源信号为  $\overline{Q}$ , $\overline{Q}_2$ ,D 和  $Q_2$ ,可重新变换 (9) 式为

$$\overline{Q}^{+} = \overline{Q}\varphi + \overline{Q}_{2}\overline{\varphi} + \overline{Q}\overline{\varphi + \varphi} \stackrel{\underline{\text{zm 3}}}{\underline{Q}_{2}} < \overline{\varphi} > \mid_{\overline{Q}} < \varphi > \mid_{\epsilon = \overline{Q}}, \tag{11a}$$

$$Q_{2}^{+} = D\varphi + Q_{2}\overline{\varphi} + Q_{2}\overline{\varphi + \varphi} \stackrel{\underline{\text{pp}} 3}{=} D < \varphi > |_{Q_{2}} < \overline{\varphi} > |_{\epsilon = Q_{2}}.$$

(11b)

根据 (11) 式画出传输门型三值伪动态 D 触发器电路图,如图 1(e) 所示,同法可得出另一种三值伪动态 D 触发器,从略。伪动态电路利用电容克服竞争冒险 (上式中的  $|_{\epsilon=\overline{Q}}$  和  $|_{\epsilon=\overline{Q}_2}$  ,它表明若过渡期短时间输出开路,但因电容而保持原信息),静态电路需利用  $A\varphi+B\overline{\varphi}=A\varphi+B\overline{\varphi}+AB$  。由此变换 (9) 式为

$$Q^{+} = \overline{\overline{Q}\varphi + \overline{Q}_{2}\overline{\varphi} + \overline{Q}\ \overline{Q}_{2}} = \overline{\overline{\overline{Q}_{2} + \varphi + Q} + \overline{Q}_{2} + \varphi}, \tag{12a}$$

$$Q_2^+ = \overline{\overline{D}\varphi + \overline{Q}_2\overline{\varphi} + \overline{D}} \,\overline{Q}_2 = \overline{\overline{\overline{Q}_2 + \varphi} + D} + \overline{Q}_2 + \varphi. \tag{12b}$$

注意:  $\varphi$  的变化发生在电路相对稳定的时刻,此时  $Q^+ = Q, Q_2^+ = Q_2$ ,而且 D 输入信号有建立时间和保持时间,在此情况下附加多余项  $\overline{Q}$   $\overline{Q}_2$  和  $\overline{D}$   $\overline{Q}_2$  可消除竞争冒险,根据上式画出三值静态 D 触发器电路图,如图 1(e) 所示,此为"或非"门型,而"与非"门型见文献 [5] . 以上由同一电路方程推出三值动态和静态 D 触发器,表明三值动态和静态电路侧向统一性的存在。另外,上述方程形式与二值电路的形式十分相似,部分地体现出二值与三值电路存在有层间统一性。综上所述,电路三要素的有机联系是客观存在的,它是建立统一性的关键。该理论和方法可以推广到四值电路,以电路三要素为基础,用五值代数工具,研究四值电路统一性,同样方法任意四值电路都可由它的函数式推出开关级结构。依此类推到多值(因信号,网络和负载是电路的基本属性,包括二值与多值电路)。

### 参 考 文 献

- [1] 吴训威. 多值逻辑电路设计原理. 杭州: 杭州大学出版社, 1994, 10, 73-120.

- [2] 方振贤, 刘莹. 完整数字电路理论和三值代数. 电子科学学刊, 1996, 18(6): 612-619.

- [3] 方振贤, 刘莹. 动态和静态电路通用设计方法. 计算机学报, 1996, 19(11): 861-866.

- [4] 吴训威,邓小卫. 三值边沿触发器的研究. 计算机学报, 1991, 14(4): 319-321.

- [5] 方振贤. 三值触发器设计及其变换, 电子学报, 1993, 21(11): 95-95.

#### TERNARY CIRCUITS AND THEORY OF THREE ESSENTIAL CIRCUIT ELEMENTS

Fang Zhenxian Liu Ying

(Department of Information and Electronic Sciences, Heilongjiang University, Haerbin 150080)

**Abstract** Based on a quaternary algebra, this paper presents a unified theory of ternary circuits—theory of three essential circuit elements (signal, network and load). The theory shows that a simple transform relation exists between ternary gate stage and switch stage, between ternary switch stage structures and between ternary dynamic and static circuits. Particularly, various ternary dynamic and static circuits can be deduced from the same equation.

**Key words** Three essential circuit elements, Quaternary algebra, Ternary dynamic and static circuits

方振贤: 男, 1936 年生, 教授, 从事数字电路理论和计算机应用的教学和科研工作.

刘 莹: 女, 1948年生, 高级实验师, 从事电子技术应用的教学和科研工作.