## 基于 FFT 的两种伪码快速捕获方案的研究与实现

李 菊 陈 禾 金俊坤 吴嗣亮 (北京理工大学电子工程系 北京 100081)

摘 要 该文提出两种基于 FFT 的伪码快速捕获方案,一种是基于分数倍采样率转换器的快捕方案;另一种是基于抽取器的快捕方案。两种伪码快捕电路均利用设计复用技术使硬件规模大幅减少;采用并行设计使系统的运算速度大大提高;采用块浮点算法以提高动态范围和运算精度。两种快捕电路均由一块 FPGA 实现。仿真和测试结果表明,基于分数倍采样率转换器的快捕电路与基于抽取器的快捕电路相比,占用的硬件资源较大,但是捕获精度更高。

关键词 快速傅里叶变换,伪码快速捕获,现场可编程门阵列,块浮点算法

中图分类号: TN911.72

文献标识码: A

文章编号: 1009-5896(2006)10-1778-04

## Two Methods of Rapid Code Acquisition Based on FFT

Li Ju Chen He Jin Jun-kun Wu Si-liang

(Department of Electronics Engineering, Beijing Institute of Technology, Beijing 100081, China)

**Abstract** Two methods of rapid code acquisition based on FFT are presented, one method is based on fractional multiple sampling rate convertor, and the other is based on decimation. To reduce hardware resource, two rapid code acquisition circuits utilizes duplicate design. Two designs applied parallel pipeline structure to improve the processing speed. Block floating-point arithmetic is used to enhance the dynamic range and computation accuracy. Two designs are implemented with a chip of FPGA respectively, simulation and measurement results show that the rapid code acquisition circuit based on fractional multiple sampling rate convertor costs more hardware resource, but can gain higher acquisition accuracy to be compared with the method based on decimation.

**Key words** Fast Fourier Transform(FFT), Rapid code acquisition, Field Programmable Gate Array (FPGA), Block floating point arithmetic

## 1 引言

扩频通信有抗干扰、抗多径衰落、可多址复用和任意选 址、高精度测量等优点。其优越性的体现是以精确的同步为 前提的,同步过程一般包括两个阶段:搜索和捕获阶段;跟 踪阶段。其中捕获是最关键的,捕获速度直接影响跟踪阶段 的性能。如何实现低信噪比条件下长序列伪码的快速捕获一 直是研究的重点,国内外有很多文献讨论过,并提出了很多 有价值的方法,如串行捕获、串并组合和并行捕获等。并行 捕获由于能在同一时间段内搜索伪码所有相位,因此捕获速 度最快。基于FFT的伪码快速捕获是并行捕获的频域实现方 法。与时域实现相比较,具有运算量小,所占用的硬件资源 少等优点。基于 FFT 的伪码快速捕获方案的核心是将基带数 字信号进行 FFT 运算,接着 FFT 结果与本地伪码 FFT 结果 进行复乘运算,再对复乘结果进行 IFFT 运算,最后对 IFFT 结果求模平方选大并进行恒虚警检测。常用的适合 VLSI 的 FFT 算法是基 2 和基 4 算法,基 2 的 FFT 算法要求处理点数 为 2" 点, 基 4 的 FFT 算法要求处理点数为 4" 点, 而基带数 字信号的采样频率往往不能满足基 2 或基 4 算法对处理点数的要求,因此在进行 FFT 运算前,需要将基带数字信号的采样频率进行转换,以满足 FFT 运算的要求。

针对这一问题,已有文献几乎都没有给出明确的解决方 案,更没有对各种方案得到的快捕结果进行分析比较,以文 献[1]为例,只是提到要对 1023 个采样点做 1024 点的 FFT, 并没有给出具体方法。因此本文提出两种基于 FFT 的伪码快 速捕获方案,并从捕获精度和硬件实现复杂度两个方面对两 种方案进行了分析和比较。一种方案是将基带数字信号通过 分数倍采样率转换单元直接转换成满足 FFT 运算要求的采 样频率;另一种方案是将基带数字信号通过抽取器将采样率 降低,然后以补零的方式达到 FFT 运算的要求。两种伪码快 速捕获电路均利用设计复用技术实现了 FFT 单元和 IFFT 单 元的复用,同时通过软件计算本地伪码 FFT,并将其结果存 储在 ROM 中,从而使硬件规模大幅减少;采用并行设计使 系统的运算速度大大提高;采用块浮点算法以提高动态范围 和运算精度。论文首先介绍了基于 FFT 的伪码快速捕获的基 本原理,接着详细论述了两种伪码快速捕获电路的结构及其 FPGA 实现,并进行了仿真和测试,最后对两者的仿真和测

试结果进行了比较和分析,然后给出结论。

#### 2 基于 FFT 的伪码快速捕获的基本原理

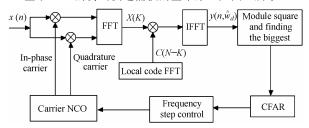

基于 FFT 的伪码快速捕获的基本原理如图 1 所示。

图 1 基于 FFT 的伪码快速捕获的原理框图

Fig.1 The principle structure of rapid code acquisition based on FFT 在采样时间  $t_n$  时刻,接收到的中频数字信号 x(n) (不考虑噪声)为

$x(n) = A \cdot \text{PN}[(1+\eta)(t_n - t_s)] \cdot \cos(\omega_l t_n + \omega_d t_n + \phi)$  (1) 其中 A 为信号幅度, $\eta$  为多普勒频移所导致的码速率变化而带来的修正系数, $t_s$  为伪码序列的起始时刻, $\omega_l$  和  $\omega_d$  分别为载波和多普勒频移的角频率, $\phi$  为初始相位。

$$X(K) = \text{FFT}\left\{x(n) \cdot \exp\left[-j(\omega_I + \hat{\omega}_d)t_n\right]\right\}, \quad K = 0, 1, \dots, N - 1 (2)$$

$$C(N-K) = \text{FFT}^* \left\{ \text{PN} \left[ (1+\overset{\wedge}{\eta})t_n \right] \right\}, \quad K = 0, 1, \dots, N-1$$

(3)

式(2)中 $\hat{\omega}_d$ 为 $\omega_d$ 的估计值,FFT 代表傅里叶变换,式(3)中 $\hat{\eta}$ 为 $\eta$ 的估计值(具体运算时可忽略不计),FFT\*代表傅里叶变换的共轭。

$y(n,\hat{\omega}_d) = \text{IFFT}\big[X(K)\cdot C(N-K)\big], \quad n=0,1,\cdots,N-1$  (4) 式(4)中 IFFT 代表傅里叶反变换。将式(2),式(3)代入式(4)中,并利用傅里叶变换性质,可得:

$$y(n, \hat{\omega}_d) = \sum_{m=0}^{N-1} x(m) \cdot \exp\left[-j(\omega_I + \hat{\omega}_d)t_m\right] \cdot \text{PN}\left[(1+\hat{\eta})(t_m - t_n)\right]$$

式(5)中 $t_n$ 为伪码序列起始时刻的估计值,与n相对应。

图 1 的工作过程就是通过在时间域  $t_n = t_0, t_1, \cdots, t_{N-1}$  和频域  $\hat{\omega}_d = \omega_{d \min}$  ,  $\omega_{d \min} + \Delta \omega_d, \cdots, \omega_{d \max}$  进行二维搜索来检测  $y(n, \hat{\omega}_d)$  的模平方是否超过由噪声统计决定的门限值,由式 (4),式(5)可知基于 FFT 的伪码快速捕获可以在给定  $\hat{\omega}_d$  下,在同一时间段内搜索伪码所有相位,因此捕获速度很高。对给定的  $\hat{\omega}_d$  ,找到  $y(n, \hat{\omega}_d)$  的模平方的最大值,并将最大值与门限值比较,如果这个最大值没有超过门限,则  $\hat{\omega}_d$  步进  $\Delta \omega_d$  ,重新计算  $y(n, \hat{\omega}_d)$  的模平方,直到找到使  $y(n, \hat{\omega}_d)$  的模平方的最大值超过门限的伪码相位 n 和多普勒频移  $\hat{\omega}_d$  ,则搜索结束,捕获完成。

#### 3 基于 FFT 的两种伪码快速捕获方案的电路设计

图 1 为传统的基于 FFT 的伪码快速捕获电路,其 FFT, IFFT 和本地伪码 FFT 均由独立的单元实现,这样整个快捕电路占用相当大的硬件资源。本文中提出的两种快捕电路均

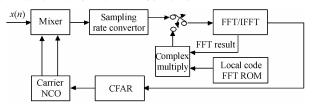

利用设计复用技术实现了 FFT 单元和 IFFT 单元的复用,同时通过软件计算本地伪码 FFT,并将其结果存储在 ROM 中,从而使硬件规模大幅减少。两种快捕电路的具体结构如图 2 所示,它们具有相同的构成单元:混频单元、采样率转换单元、FFT/IFFT 单元、复乘单元、本地伪码 FFT 结果存储单元、恒虚警检测单元和载波 NCO 单元。唯一不同的是采样率转换单元的具体实现:一种方案是利用分数倍采样率转换完成基带数字信号采样频率的转换,以满足 FFT 运算的要求;另一种是将基带数字信号通过抽取器将采样率降低,然后以补零的方式达到 FFT 运算的要求。

图 2 基于 FFT 的两种伪码快捕电路结构框图

Fig.2 The structure of two rapid code acquisition circuit based on FFT

图 2 的工作过程如下: 数字中频输入信号 x(n),与载波 NCO 输出的同相和正交相载波进行混频后,输入到采样率转 换单元,得到满足FFT运算要求的基带信号输出给FFT/IFFT 单元进行 FFT 运算。FFT 结果与本地伪码 FFT 结果在复乘单 元进行复乘运算。复乘结果输出到 FFT/IFFT 单元进行 IFFT 运算。IFFT 结果在恒虚警检测单元先进行求模平方选大,然 后对最大值两侧的一段数据求和取平均,再将均值乘上由虚 警概率决定的系数以求出该次判决的门限值。模平方最大值 与门限值进行比较,比较的结果送给载波 NCO 单元,用来 决定频率是否步进。如果模平方最大值没有超过门限值,则 频率步进,重复上述搜捕过程;否则搜索结束,捕获成功, 模平方最大值对应的点数就是伪码起始相位,载波 NCO 的 频率控制字对应载波加多普勒频移。由于混频单元、复乘单 元、本地伪码 FFT 结果存储单元和恒虚警检测单元比较简单 并且在上面的叙述中已经介绍, 因此下面详细介绍采样率转 换单元、FFT/IFFT 单元和载波 NCO 单元、。

#### 3.1 采样率转换单元设计

(5)

3.1.1 分数倍采样率转换器设计 分数倍采样率转换器完成 I/D 倍采样率转换,以使混频后的信号经过此单元后得到满足 FFT 运算要求的基带信号。由于时变网络结构克服了多项结构分数延迟的问题,并且结构简单、高效,因此论文中采用时变网络结构来实现此 I/D 倍采样率转换,其输入输出关系为

$$y(n_2T_2) = \sum_{k=0}^{Q-1} x \left[ \left( \left\lfloor \left( n_2 D \right) / I \right\rfloor - k \right) T_1 \right] h \left[ \left( n_2 D \oplus I + kI \right) T_3 \right]$$

(6)

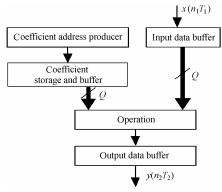

式中 $\lfloor (n_2D)/I \rfloor$ 是对  $(n_2D)/I$  的商数下取整,  $n_2D \oplus I$  是  $(n_2D)/I$  的余数, Q = N/I , N 为滤波器  $h(rT_3)$  的长度。分数倍采样率转换器的结构如图 3 所示。

图 3 分数倍采样率转换器的结构框图

Fig.3 The structure of fractional multiple sampling rate convertor

整个设计由 6个单元组成: 时钟产生单元、系数地址产生单元、系数存储和缓冲单元、输入数据缓冲单元、运算单元及输出数据缓冲单元。时钟产生单元产生各单元工作所需时钟; 系数地址产生单元由一个最大计数为 N-1 的计数器构成,循环产生系数地址 0 到 N-1; 系数存储和缓冲单元用于存储滤波器系数,并按系数地址将滤波器系数顺序读出,再通过 Q = N/I 级缓存,将一路系数输出转换为 Q 路系数输出,滤波器系数在存储器中每 Q 个一组,按式(6)中  $n_2D \oplus I$  的顺序存放。图 3 的工作过程如下:输入数据  $x(n_1T_1)$  经输入数据缓冲单元后,产生计算一个输出所需要的 Q 路数据,并将它们送到运算单元,与此同时,Q 路滤波器系数也进入运算单元,与 Q 路输入数据进行相应的乘加运算,乘加的结果经输出数据缓冲单元后即得到输出  $y(n_2T_2)$ 。

3.1.2 抽取器设计 令式(6)中内插因子 I = 1,则得到抽取因子为 D 的抽取器的输入输出关系为

$$y(n_2T_2) = \sum_{k=0}^{N-1} x \left[ (n_2D - k)T_1 \right] h(kT_1)$$

(7)

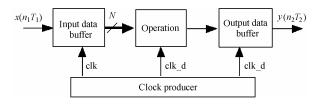

式中 N 为抗混叠滤波器  $h(kT_1)$  的长度。抽取器的结构如图 4 所示。抽取器由 4 个单元组成:时钟产生单元、输入数据缓冲单元、运算单元和输出数据缓冲单元。时钟产生单元产生各单元的工作时钟, $clk_d$  为 clk 的 D 分频时钟。图 4 的工作过程如下:输入数据  $x(n_1T_1)$  经输入数据缓冲单元后,产生计算一个输出所需要的 N 路数据,并将它们送到运算单元,与 N 路滤波器系数进行相应的乘加运算,乘加的结果经输出数据缓冲单元后即得到输出  $y(n_2T_2)$ 。

#### 3.2 FFT/IFFT 单元设计

由于 FFT 和 IFFT 的运算结构完全相同,唯一不同的是

图 4 抽取器的结构框图

Fig.4 The structure of decimation

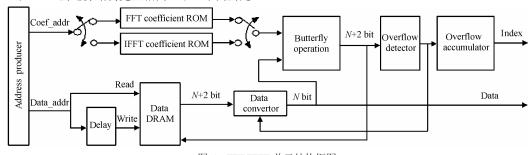

旋转因子互为共轭,因此采用同一个处理单元来实现 FFT 和IFFT 运算,只是采用不同的旋转因子,这样可以大大的节省硬件资源。FFT/IFFT 单元采用递归结构的基 2FFT 算法,并用正序输入、逆序输出、按时间抽取的原址运算方法设计实现。该单元采用块浮点算法实现基 2FFT 运算,块浮点算法相对定点运算有较高的精度,相对浮点运算硬件结构简单,是定点和浮点运算的折衷,从而使 FFT/IFFT 单元兼具高速和高精度的特点。FFT/IFFT 单元结构如图 5 所示。

图 5 的工作过程如下: 地址产生单元分别产生旋转因子地址和数据地址,直接送给数据双端口 RAM 的地址是读原始数据和各级蝶形运算结果的地址; 经延迟单元后送给数据双端口 RAM 的地址是写各级蝶形运算结果的地址; 蝶形运算单元接收来自旋转因子 ROM 的旋转因子和来自数据双端口 RAM 的数据完成基 2FFT 的蝶形运算;各级蝶算输入为 N位,输出为 N+2 位;溢出检测单元根据各级蝶算结果的高三位判断该级蝶算的溢出,并送给数据转换单元和溢出累加单元;数据转换单元根据各级溢出从 N+2 位结果中取出 N 位以送给蝶算单元; 溢出累加单元对各级溢出进行累加得到FFT/IFFT 结果的指数,指数和最后一级数据共同构成FFT/IFFT 单元的输出。

#### 3.3 载波 NCO 单元设计

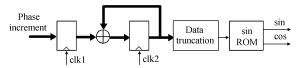

载波 NCO 单元接收恒虚警检测单元输出的模平方最大值与门限值比较结果,以决定搜索频率是否步进,并输出相应频率的同相和正交相载波。载波 NCO 的结构如图 6 所示。

相位增量值在 clk1 作用下进行锁存(即把最新搜索频率对应的频率控制字置入寄存器中),然后在 clk2 作用下进行相位累加,累加结果经数据位截取后输出到正弦查找表单元,以得到正弦和余弦输出。其中相位累加器字长  $B_{\theta(n)}$  由下式决定:

图 5 FFT/IFFT 单元结构框图 Fig.5 The structure of FFT/IFFT

图 6 载波 NCO 的结构框图 Fig.6 The structure of carrier NCO

$$B_{\theta(n)} = \log_2^{\left[\frac{f_{\text{clk2}}}{\Delta f}\right]} \tag{8}$$

式中  $\Delta f$  为频率分辨率,  $f_{clk2}$  为 clk2 的时钟频率。

# 基于 FFT 的两种伪码快速捕获电路的 FPGA 实

当伪码选择速率为 1.023MHz 的 C/A 码,输入信号的多 普勒频率设置为 2kHz, 伪码延时设置为 0.51124ms 时, 软件 仿真和硬件实现的结果如 4.1 节和 4.2 节所述。

#### 4.1 软件仿真

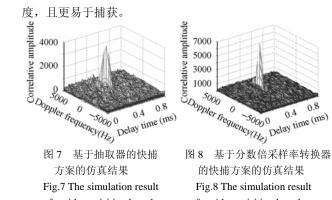

两种伪码快捕方案的 Matlab 仿真结果如图 7 和图 8 所 示。

图 7 为基于抽取器的快捕方案的仿真结果: 捕获到的多 普勒频率为 2kHz, 伪码延时为 0.51147ms, 相关幅度(模)的 最大值为3571.4。图8为基于分数倍采样率转换器的快捕方 案的仿真结果; 捕获到的多普勒频率为 2kHz, 伪码延时为 0.51123ms,相关幅度(模)的最大值为6354.5。由软件仿真结 果可以看出:基于分数倍采样率转换器的快捕方案的伪码延 时误差比基于抽取器的快捕方案的伪码延时误差小 0.00022ms, 仅为 0.00001ms, 且模的最大值有 2.5dB 的增益。 因此基于分数倍采样率转换器的快捕方案有更高的捕获精 度,且更易于捕获。

Fig.7 The simulation result of rapid acquisition based on decimation

的快捕方案的仿真结果 Fig.8 The simulation result of rapid acquisition based on fractional multiple sampling rate convertor

### 4.2 FPGA 实现

FPGA 选择 Xilinx 公司 Virtex-II 系列产品 XC2V3000-5, 整个设计采用 Verilog 语言自顶向下方式描述,运算位数为 12位,经过仿真、综合、映射、布局、布线及带有时延的后 仿真,两种伪码快捕电路的实现结果如表1所示。

从表1可以看出,两种伪码快捕方案的硬件电路均达到 设计要求,且基于分数倍采样率转换器的快捕电路比基于抽 取器的快捕电路占用更多的硬件资源。由于两种快捕电路除 采样率转换单元的具体实现不同外, 其它单元的结构均相

表 1 两种伪码快捕电路的 FPGA 实现

Tab.1 The realization of two rapid code acquisition

|        | 基于抽取器     | 基于分数倍采样率  |

|--------|-----------|-----------|

|        | 的快捕电路     | 转换器的快捕电路  |

| 芯片利用率  | 19%       | 26%       |

| 最高工作频率 | 58.387MHz | 58.059MHz |

| 模的最大值  | 3530.5    | 6312.1    |

| 多普勒频率  | 2kHz      | 2kHz      |

| 伪码延时   | 0.51147ms | 0.51123ms |

同,因此表1中芯片利用率的不同体现的就是分数倍采样率 转换器和抽取器的硬件实现的不同, 即分数倍采样率转换器 占用更多的硬件资源,结构更复杂。

#### 结束语 5

基于 FFT 的两种伪码快速捕获方案由于能在同一时间 段内搜索伪码所有相位, 因此捕获速度很高, 两种快捕电路 均利用设计复用技术使硬件规模较传统快捕电路大大减少, 且易于实现。软件仿真和硬件实现的结果表明,基于分数倍 采样率转换器的快捕电路与基于抽取器的快捕电路相比,占 用的硬件资源较大,但是捕获精度更高,并且模的最大值有 2.5dB 的增益,非常有利于低信噪比条件下的伪码快速捕获。

#### 参考文献

- Alaqeeli A, Starzyk J. Real-time acquisition and tracking for GPS [1] receivers[C]. International Symposium on Circuits and Systems, Bangkok, 2003: 500-503.

- Liu Yun-fei, Chen Zhi-jun. Implement and performance analysis of PN code acquisition based on FFT[C]. Fifth World Congress on Intelligent Control and Automation, Hangzhou, 2004: 5399-5401.

- Kang S, Lee Y H. Rapid acquisition of PN signals for DS/SS systems using a phase estimator[J]. IEEE Journal on Selected Areas in Communications, 2001, 19 (6): 1128-1137.

- Jari H J Iinatti. On the threshold setting principles in code acquisition of DS-SS signals[J]. IEEE Journal on Selected Areas in Communications, 2000, 8 (1): 62-72.

- Mark L, Psiaki. Block acquisition of weak GPS signals in a software receiver[C] ION GPS-2001, Sept.11-14, 2001: B6, 2838-2850.

- Rappaport S S, Grieco D M. Spread-spectrum signal acquisition: Method and technology[J]. IEEE Communications Magazine, 1984, 22 (6): 6-22.

- 女,1977年生,博士生,研究方向为数字信号处理、集成 电路设计等.

- 女,1970年生,副教授,主要研究方向为ASIC设计、VLSI 禾: 并行算法与结构、高速信号处理、可靠性设计等.

- 金俊坤: 男,1970年生,博士生,研究方向为扩频接收机技术、雷 达信号处理等.

- 吴嗣亮: 男, 1964年生, 教授, 主要研究方向为现代信号处理, 雷 达信号处理等.