# 高清晰度电视视频解码器系统控制的设计与实现「

刘健 李 华 王承宁 俞斯乐 (天津大学电子信息工程学院 天津 300072)

摘 要 该文提出了一种高清晰度电视(HDTV)视频解码器系统控制的设计方案,并对其工作原理进行 了阐述,该方案采用 FPGA (现场可编程门阵列) 技术实现,具有设计灵活、方便的特点,经整机联试系统控 制工作稳定、可靠,保障了正常的解码和显示。

高清晰度电视 (HDTV), 系统控制, MPEG-2, FPGA 关键词

中图号 TN941

### 1 引 言

作为新一代的电视广播系统,数字高清晰度电视不仅可以得到更高的图像质量,更好地满 足人眼的视觉特性,更高的信道利用率,更重要的是促进了广播电视与通信及计算机业务一体 化的进程。数字高清晰度电视在世界上越来越受到关注,是目前广播电视事业发展的方向。它 是数字信号处理和超大规模集成电路技术发展到一定阶段的产物,是近年来国际科技界一大热 点研究领域。包括中国在内的许多国家,纷纷开展了对高清晰度电视硬件实现方法的研究。美 国最先研制成功数字高清晰度电视功能样机,我国也于1998年9月顺利完成数字高清晰度电 视功能样机系统的地面广播开路实验,成为继美国、欧洲、日本之后第四个研制成功的数字高 清晰度电视功能样机的国家,本文着重分析视频解码器系统控制的功能、构成及其工作原理, 在此基础上设计并采用现场可编程门阵列 FPGA 实现。

#### 2 系统控制的功能和构成

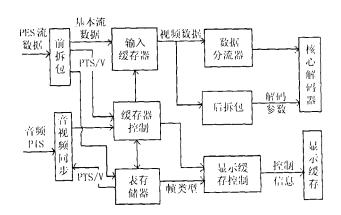

HDTV 视频解码器系统控制是连接解复用和核心解码器的接口,完成数据拆包、数据缓存、 音视频同步及显示缓存控制等重要的工作, 对保障解码端的正常解码和显示起着至关重要的作 用。本文提出了一套系统控制的构成方案, 其构成如图 1 所示:

图 1 系统控制构成的原理框图

<sup>1 2000-04-28</sup> 收到、 2000-12-04 定稿 98 年国家重大科技产业工程项目

系统控制中数据拆包、缓存器控制、音视频同步及显示缓存控制等几个部分都是比较复杂的控制技术。本文综合现场可编程门阵列 FPGA 的特点和解码器系统的实际需要,通过理论分析和计算机仿真,针对以上难题提出解决方案并在实践中加以验证。下面我们就系统控制各部分的构成、工作原理及其 FPGA 实现进行详细介绍。

#### 3 各部分的工作原理

3.1 拆包处理 拆包主要包括拆 PES(Packet Element Stream) 包 (前拆包) 和拆视频头 (后拆包) 两部分。 HDTV 视频解码器系统控制器接收来自解复用器的视频打包基本流 (简称 PES 流) 数据,其码流格式符合 MPEG-2 系统层标准。拆 PES 包是把输入的 PES 流分解成两部分: 一部分是 PES 头,可从中提取码流中的系统层信息 (包括视频 PTS(Presentation Timing Stamp) 值,用以恢复音视频的同步) 和帧编码类型信息 (实现显示缓存的控制)。这些帧的特征参数被暂存在表存储器中,当帧同步信号到来时读出;另一部分是符合 MPEG-2 MP@H-1440级标准的图像编码数据,这部分数据被暂存在输入缓存器中,并在相应的解码时刻逐帧移出缓存器,送到视频解码器的核心解码单元以解出图像数据。而拆视频头是对编码层中的头信息进行提取,给核心解码器解码提供必要的解码参数。

由于 PES 包和各视频头的结构按照 MPEG 标准的规定都是固定格式的,因此拆包处理又称为定长解码,实现它的关键是如何快速、准确地找到相应的头起始码,然后,就可以在码流的确定位置提取到所需的 PES 头信息或视频头信息,并准确地分离出视频基本数据流。

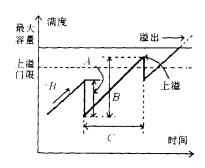

3.2 输入缓存控制 输入缓存器对解复用输出的串行数据进行缓存,然后再以帧为单位输送给核心解码器。在这个过程期间不允许出任何差错,任何微小的差错都有可能对核心解码器造成灾难性的影响。系统控制采用 8M SRAM 作为输入缓存。在缓存器控制中尤其需要注意的是上下溢的问题。在通常情况下,输入缓存器永远不会发生溢出或下溢。然而,对于一个实际解码器、当输入的数据流没有严格按照 MPEG 标准正确编码或输入缓存器的输入速率与输出速率不相等时,就会发生溢出或者下溢。输入缓存器的基本操作如图 2 所示。图中 A 为一帧数据量大小, B 为一帧时间内写入缓存器的数据量, C 为帧周期, R 为输入码率。

图 2 输入缓存器的基本操作

因为数据的溢出会对图像解码造成灾难性的损失,所以必须避免溢出的发生。上溢和下溢是否发生是通过预定的门限来判断的。当门限被超过时,判定缓存器如果发生了上溢,控制缓存器跳过当前帧甚至下一帧来降低缓存器的充满度,以确保缓存器内有足够的空间来存储后续输入的数据,当缓存器发生上溢时,跳帧应当本着 I 帧 P 帧不能跳, B 帧可以跳的原则;如果发生了下溢,则暂停不读,以确保缓存器有足够的时间来存储后续输入的数据。

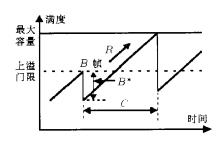

上溢门限确定的准则是:保证存储器从当前时刻到下一个帧同步到来之前不会发生溢出。门限值应定得恰到好处,如果门限值过高,则起不到抑制缓存器溢出发生的作用;如果门限定低了,缓存器就会频繁的出现上溢,经常发生跳帧会明显影响图像的显示质量。根据缓存器的工作情况,在假定缓存器恰好不溢出前提下,如图 3 所示,图中  $B^*$  为 B 帧最小数据量,C 为帧周期,B 为输入码率。上溢门限计算公式为

上溢门限 = 最大容量 - 输入码率 × 帧周期 +B 帧最小数据量 (Mbit)

下溢门限的确定相对较为简单,在每一个帧同步到来时,如果此时存储器中的数据量不足一个整帧,则认为发生了下溢,暂停读出数据,并向后拆包单元、核心解码器及显示缓存发出暂停解码,重复显示上一帧图像的信号,等候下一个帧同步的到来。

图 3 上溢门限的确定

3.3 音视频同步 音视频同步是 MPEG 系统中一项很复杂的控制技术, 也是 HDTV 中一项非常重要的技术。同步的好坏将直接影响 HDTV 系统的视听效果。

在解码端音频和视频存取单元分别经过缓存,解码,显示的过程是相对独立的,在实际解码系统中音频解码器与视频解码器的状态有可能存在着较大的差异。为了避免这种情况的发生,解码端可以根据音频和视频存取单元的 PTS 信息,采取措施调整解码器状态,保证视频音频的同步。

通常实现音视频同步的方式有两种:一种是以视频为基准,通过重复或跳音频帧的方法来调整音视频同步;另一种则反之,以音频为基准,通过对视频帧跳帧与重复显示来完成。由于我们的 HDTV 功能样机系统中采用音频不动,通过视频帧的调整来保证音频视频同步,而且考虑到音频帧一般较小,不会发生溢出,而视频解码器一般变化较大,且变动视频帧不会明显影响显示效果,因此本系统采用后一种方法。

具体实现时,解码端由节目时钟参考 (PCR) 恢复出与编码端同步的系统时钟,在解码端建立一个局部记数器,计数时钟为系统时钟。当视频数据输出前,从表存储器读出视频 PTS 与计数器的结果相比较,若相当,则同步,否则失步,进行视频帧的等待或跳帧。

3.4 显示缓存控制 显示缓存控制部分的主要功能是完成图像解码顺序与显示顺序的重排。 在有 B 帧存在的情况下,图像的编码顺序与显示顺序是不同的,显示缓存控制就是对显示缓存部分的显示状态进行控制、保证图像的连续播放。

系统控制可根据 PTS 和 DTS(Decoding Time Stamp) 的值来控制。因为 DTS 是解码时间标志,各帧的 DTS 值按输入的顺序依次递增; PTS 是显示时间标志,是各帧重排序后的显示时间。也可以根据当前显示缓存的状态和当前要写入显示缓存的帧的类型来控制。前一种方法实现起来比较复杂,因为使用 PTS 和 DTS 值就要牵扯到本地系统时钟参考的问题,而且还得考虑系统的延时等,比较复杂;后一种方法实现起来比较容易,但在设计上有一定难度。

显示缓存由 VRAM 构成,仅需二个帧存器便可以实现。写入原则是:读哪个缓存器则往哪个缓存器中写,写入依帧一、帧二次序进行。读出原则是:是 B 帧则直接读出;有两个 I 帧或 P 帧时,先进的先出。根据以上原则,通过推导,可以把显示缓存的情况归纳成几种状态,对应每种状态和输入帧类型,各显示缓存的读写控制信号是固定的可用状态机实现显示缓存的控制。

#### 4 系统控制的 FPGA 实现

本系统选用了美国 ALTERA 公司 FLEX10K 系列的 EPF10K50RC-3 型芯片为主要工作芯片, FLEX10K 器件由两部分组成,一部分是嵌入式阵列 (EAB),可以用来实现存储器和特定逻辑功能,系统中表存储器及部分前拆包功能就是利用这种结构实现的;另一部分是逻辑阵列 (LAB),可以用来实现常用逻辑。

前拆包单元完全在 FPGA 内部实现,实现前拆包的难点有两点:一是实时性,即需要对解 复用输出的码流实时监测并随之产生相应的动作,这就需要 FPGA 的内部延时特性要限制在工作时钟频率范围之内,本系统时钟是 27MHz,对于所选用的 FPGA 芯片来说是完全可以实现的,二是前拆包处于系统控制单元的最前端,其功能很有可能随着环境的需要而扩充或完善,而

FPGA 的可编程特性则可以保证在无须对整个系统做大的变动的情况下在短时间内完成功能的扩充或完善,这一点对整个系统的性能是至关重要的。

输入缓存器的读写控制信号都是由 FPGA 产生的。上下溢控制要通过高位加减法运算来判断是否发生了上下溢,ALTERA 公司的开发系统提供的库函数中包含这个功能,我们直接调用库中的功能模块来实现上下溢控制,实践证明它工作得很好,省却了大量繁琐的设计工作。音视频同步的比较、判断及同步的调整也是通过 FPGA 控制实现的。显示缓存重排序是由 FPGA的状态机实现的,并用 AHDL 语言描述。

## 5 结 束 语

以上分析了 HDTV 视频解码器系统控制的功能、构成方案,并详细分析了各部分的工作原理及其 FPGA 实现,按照以上方案设计的电路已成功地应用于我国独立开发和研制的"数字高清晰度电视功能样机系统"中。

由于采用现场可编程器件 FPGA 实现,且设计完全符合 MPEG-2 标准的要求,因此,这一设计方案具有很好的灵活性和通用性,可方便地实现对现有功能的修改和扩充,还可以方便地集成到 ASIC 中,有利于 HDTV 的产业化发展。

# 参 考 文 献

- ISO/IEC 13818-1 Generic Coding of Moving Pictures and Associated Audio Information: System, Jan. 20, 1995.

- [2] ISO/IEC 13818-2 Generic Coding of Moving Pictures and Associated Audio Information: Video, Jan. 20, 1995.

- [3] ATSC: ATSC Digital Television Standard, Oct. 4, 1995.

- [4] ATSC: Guide to the Use of the ATSC Digital Television Standard, Oct. 4, 1995.

- [5] K. Kawahara, H. Yamauchi, S. Okada, A single chip MPEG1 decoder, IEEE Trans. on Consumer Electronics, 1995, 41(3), 707–715.

- [6] Aldo Cugnini, Richard Shen, MPEG-2 video decoder for the digital HDTV grand allance system, IEEE Trans. on Consumer Electronics, 1995, 41(3), 748-752.

# DESIGN AND IMPLEMENTATION OF SYSTEM CONTROL FOR THE HDTV VIDEO DECODER

Liu Jian Li Hua Wang Chengning Yu Sile

(School of Electronic Information Engineering, Tianjin University, Tianjin 300072, China)

Abstract This paper presents the design and implementation of system control for HDTV video decoder. The principle of the system control is described in detail too. FPGA is adopted for its programmable and reconfigurable features. The system control works perfectly and steadily which ensures the perfect work of decoder and display buffer.

Key words High Definition Television (HDTV), System control, MPEG-2, FPGA

刘 健: 男, 1973年生, 助教, 主要研究方向有: 数字视频技术, 数字图像处理等.

李 华: 女, 1942 年生, 教授, 博士生导师, 主要研究方向有: 数字图像处理, 数字电视技术等.

王承宁: 男, 1972年生, 讲师, 主要研究方向有: 数字视频技术, 数字图像编码等.

俞斯乐: 男,1930年生,教授,博士生导师,主要研究方向有:数字视频技术,数字图像编码等.