Jul. 2017

# 自偏置 PLL 电源噪声敏感度分析

摘 要:该文提出一种基于传递函数的有效方法,可以预测自偏置 PLL 电源噪声引起的抖动性能。PLL 的复制偏置调整器的电源噪声敏感度由小信号分析提取,分析表明需要在闭环带宽和电源噪声敏感度之间做权衡。作为例子,该文分析了一款具体的自偏置 PLL 电路的电源噪声性能,该 PLL 为一款相位插值 CDR 提供时钟。所提方法与瞬态仿真的结果进行了对比,结果表明该方法可以预测周期抖动数值,具有相当精度。同样,该方法也对提高自偏置 PLL 噪声性能有指导意义。

关键词: 电源噪声抑制: 自偏置 PLL: 噪声传递函数: 周期抖动

中图分类号: TN86 文献标识码: A 文章编号: 1009-5896(2017)07-1646-05

**DOI**: 10.11999/JEIT161088

# Sensitivity Analysis of Power Supply Noise Induced Jitter in Self Biased PLL

LI Tianyi<sup>©2</sup> XU Xiaodong<sup>©</sup> YIN Tao<sup>©</sup> WEI Yuanfeng<sup>©2</sup>

HUANG Guocheng<sup>©</sup> LI Wei<sup>©</sup> YANG Haigang<sup>©</sup>

(Institute of Electronics, Chinese Academy of Sciences, Beijing 100190, China) (University of Chinese Academy of Sciences, Beijing 100049, China)

Abstract: This paper presents an effective method based on transfer function to predict the jitter performance of self biased PLL due to power supply noise. The supply noise sensitivity of replica biased regulator of PLL is derived from small signal analysis. The analysis shows that there exist tradeoffs between the closed-loop bandwidth and supply noise sensitivity of regulator. As an example, the supply noise performance of one specific self biased PLL which is used as a clock generator in PI based CDR is analyzed. The comparison between transient simulation method and the proposed method is made. The results show that the proposed method can predict the value of period jitter with considerable accuracy. It can also give guidelines on how to further improve the noise performance of SBPLL.

Key words: Supply noise rejection; Self biased PLL; Noise transfer function; Period jitter

## 1 引言

自偏置相位锁定环(SBPLL)<sup>[1-6]</sup>广泛应用于各种应用中,如频率合成器、时钟歪斜(skew)消除、时钟数据恢复(CDR)以及抖动滤波等。它可以在不同工艺-电压-温度(PVT)条件下以及输出频率大范围变化时调整环路动态参数。当PLL用作时钟产生电路时,对低频时钟倍频产生高频时钟,主要受大规模数字电路的同步开关切换引起的电源噪声影响,随着CMOS工艺尺寸的不断缩小而愈加明

显<sup>[7-11]</sup>。电源噪声可以耦合到压控振荡器(VCO)的控制电压上,恶化PLL输出时钟的相位噪声和抖动。携带高频噪声的时钟进一步减小了传输系统的噪声容限,降低了误码率。

前人对 SBPLL 的电源噪声抑制(SNR)分析如下。文献[1]分析了作为 SBPLL 中 VCO 的延时单元的对称负载的电源噪声敏感度,然而没有包含 SBPLL 的整体噪声性能分析。文献[6]用系统传递函数估算了 PLL 内部电路噪声,但没有考虑电源噪声影响,并且同样没有考虑自偏置结构带来的变化。传统方法如瞬态仿真应用于评估 PLL 抖动性能<sup>[12-14]</sup>,但过于繁琐费时,更重要的是没有探究如何提升抖动性能。本文提出了一种有效的 SBPLL电源噪声敏感度评估方法,假设 SBPLL 为线性系统

收稿日期: 2016-10-17; 改回日期: 2017-02-10; 网络出版: 2017-03-21 \*通信作者: 杨海钢 yanghg@mail.ie.ac.cn

基金项目: 国家自然科学基金(61271149, 61474120)

Foundation Items: The National Natural Science Foundation of China (61271149, 61474120)

— 在 PLL 锁定状态下是合理的<sup>[15]</sup> — 并且应用噪声传递函数分析电源噪声敏感度。同时可以预测 SBPLL 的周期抖动,以便定量评估抖动改善的程度。

本文构成如下:第2节介绍了本文方法的原理,第3节给出仿真结果,第4节总结全文。

#### 2 本文提出的方法

#### 2.1 SBPLL 的噪声传递函数

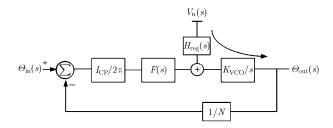

原则上 SBPLL 可以视作理想二阶电荷泵 (CP)PLL。图 1 所示为传统二阶 CP PLL 的小信号模型。 $H_{\text{reg}}(s)$ 是 VCO 调整器电路的传递函数, $V_{\text{n}}(s)$ 是电源噪声,F(s)是环路滤波器的传递函数。由  $V_{\text{n}}(s)$ 到  $\theta_{\text{out}}(s)$ 的噪声传递函数如式(1)所示<sup>[15]</sup>。

$$\begin{split} H_{\mathrm{n}}(s) &= \frac{\theta_{\mathrm{out}}(s)}{V_{\mathrm{n}}(s)} = \frac{sH_{\mathrm{reg}}(s)K_{\mathrm{VCO}}}{1 + \frac{K_{\mathrm{VCO}}I_{\mathrm{CP}}F(s)}{2\pi Ns}} \\ &= \frac{sH_{\mathrm{reg}}(s)K_{\mathrm{VCO}}}{s^2 + 2\zeta\omega_{\mathrm{n}}s + \omega_{\mathrm{n}}^2} \\ &\stackrel{\sharp}{=} \frac{1 + sRC}{sC} \; , \quad \omega_{\mathrm{n}} = \sqrt{\frac{I_{\mathrm{CP}}K_{\mathrm{VCO}}}{2\pi CN}} \; , \quad \zeta = \frac{R}{2}\sqrt{\frac{I_{\mathrm{CP}}CK_{\mathrm{VCO}}}{2\pi N}} \; . \end{split}$$

若不存在 VCO 调整器电路, $H_{\text{reg}}(s)$ 为 1,全部电源噪声将传递到 VCO 的控制电压上, $H_{\text{reg}}(s)$ 的峰值频率接近 PLL 的自然频率  $\omega_{\text{n}}$ ,此时 SNR 恶化。SBPLL 中加入了复制偏置电路 (replica biasing circuit)作为调整器,以提升抖动性能。

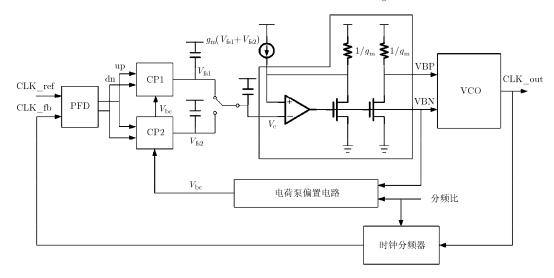

#### 2.2 SBPLL 的复制偏置调整器电路

图 2 所示为文献[2]中采用的 SBPLL 电路,CP1 和 CP2 为两个相同的电荷泵,对各自的电容充电, $V_{\rm fs1}$  和  $V_{\rm fs2}$  分别为两个电荷泵产生的控制电压。一个单刀双掷开关在 CP1 和 CP2 的输出之间切换,以保证开关右侧电压不会突变,并通过采样滤波网络

图 1 SBPLL 的小信号模型框图

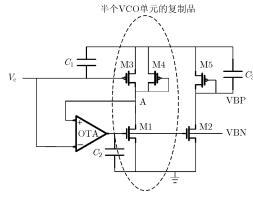

减小定性抖动的影响,产生控制电压 $V_c$ 。控制电压 $V_c$ 经过线框中复制偏置调整器电路的处理产生两个偏置电压 VBP 和 VBN,前者为 VCO 的 PMOS 负载提供偏置,后者则为 VCO 的尾电流源提供偏置。在锁定状态下, $V_c$ , $V_{\rm fal}$  和 $V_{\rm fal}$  相等,因而只分析复制偏置调整器电路,如图 3(a)所示,M3 和 M4 是 VCO 对称负载的一半复制品。相位误差信息储存在 $C_1$ 中,由电荷泵电流充电到电压 $V_c$ ,由跨导运算放大器(OTA)和 M1 构成的负反馈回路保证 A 点电压与 $V_c$  相等。电容  $C_2$ 用于环路补偿,VBP 和 VBN 用于为 VCO 提供偏置。电容  $C_p$ 表示寄生电容,如 OTA 固有的栅极电容,由导线连接到 $V_c$ 。已知对称负载 R 和 $V_{\rm dd}$  — VBP 成反比[2],因此电源噪声敏感度可以由 $V_{\rm dd}$  — VBP 和 $V_{\rm dd}$  的比值来决定。

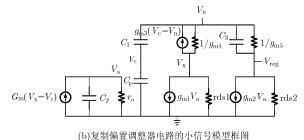

SBPLL 的复制偏置调整器的小信号模型如图 3(b)所示, $G_m$ 为 OTA 的等效跨导, $r_o$ 为 OTA 的输出阻抗。值得一提的是当 PLL 在锁定状态下,电荷泵开关只在参考时钟周期的一小部分时间内开启,因此假设  $V_c$  点开路是合理的。整个电路有两个重要的极点,一个在 OTA 的输出端,另一个在  $V_{reg}$  。由于 OTA 的高输出阻抗,OTA 输出端的极点是主导极点。A 点的极点为  $g_{m4}/C_{gs4}$ ,由于过高可以忽略。因此从  $V_n - V_{reg}$ 到  $V_n$  的传递函数如式(2)所示。

图 2 文献[2]中的 SBPLL 电路结构

(a) SBPLL复制偏置调整器电路原理图

图 3 复制偏置调整器电路原理图及小信号模型

$$\begin{split} H_{\text{reg}}(s) &= \frac{V_{\text{n}} - V_{\text{reg}}}{V_{\text{n}}} \\ &= \frac{1 + yA_{0} + \frac{C_{\text{p}}}{C_{1}} zA_{\text{a}}A_{0}^{2}}{\left(1 + xA_{0} + sC_{3}r_{\text{ds2}}\right) \left(1 + yA_{0} + \frac{A_{0}A_{\text{a}}}{1 + sC_{2}r_{\text{o}}}\right)} (2) \end{split}$$

其中,  $A_0\!=\!g_{\mathrm{m}1}r_{\mathrm{ds}1}\!=\!g_{\mathrm{m}2}r_{\mathrm{ds}2},\; A_{\mathrm{a}}=G_{\mathrm{m}}r_{\mathrm{o}},\; x=g_{\mathrm{m}5}/g_{\mathrm{m}2}, \ y=g_{\mathrm{m}4}/g_{\mathrm{m}1},\; z=g_{\mathrm{m}3}/g_{\mathrm{m}1}$ 。

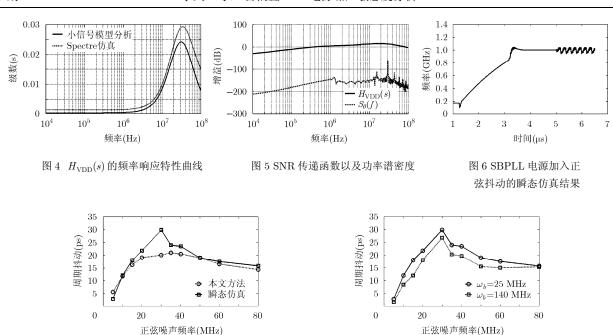

$A_0$ 是 NMOS 的本征增益, $A_a$ 是 OTA 的直流 (DC)增益。图 4 所示为小信号分析和 spectre 仿真的结果对比,两结果十分吻合。

可见DC下SNR主要取决于 $C_p/C_1$  的值,本质在于尽可能降低 $C_p$  以达到良好的SNR。当频率达到OTA的带宽时,OTA的增益开始下降,而SNR以20dB/dec的速度跌落。因此需要权衡SNR和环路稳定性,为了在宽频率范围内维持良好的SNR水平,OTA的带宽必须最大化。闭环带宽 $G_m/C_2$  与OTA极点成正比,而反馈环路的相位裕度和OTA带宽成反比。

#### 2.3 预测 SBPLL SNR 的方法

调整器电路的传递函数  $H_{reg}(s)$  已知后,可以计算出 SBPLL 的噪声传递函数  $H_{VDD}(s)$  ,如式 $(3)^{[15]}$ :

$$H_{\mathrm{VDD}}(s) = \frac{\theta_{\mathrm{out}}(s)}{V_{\mathrm{DD}}(s)} = \frac{\theta_{\mathrm{out}}(s)}{V_{\mathrm{reg}}(s)} \frac{\theta_{\mathrm{reg}}(s)}{V_{\mathrm{DD}}(s)} = H_{\mathrm{reg}}(s) H_{\mathrm{n}}(s) \left(3\right)$$

从而 $\theta_{\rm out}$ 的功率谱密度为

$$S_{\theta}(f) = \overline{V_{\rm DD}^2(f)} \left| H_{\rm reg}(f) H_{\rm n}(f) \right|^2 \tag{4}$$

其中, $\overline{V_{\rm DD}^2(f)}$  为电源噪声的功率谱密度。

图 5 所示为 SBPLL 的  $H_{VDD}(s)$  和  $S_{\theta}(f)$  的例子。 若已知  $S_{\theta}(f)$ ,相位噪声和抖动累积<sup>[16]</sup>之间的关系可以用于预测 SBPLL 的 N 周期抖动  $J_{c}(N)$ ,如式(5):

$$J_{c}(N) = 2\left(\frac{T_{0}}{\pi}\right)^{2} \int_{0}^{+\infty} S_{\theta}(f) \sin^{2}\left(\pi f N T_{0}\right) \mathrm{d}f \tag{5}$$

其中, $T_0$ 是SBPLL输出时钟的周期。

### 3 仿真结果

本文提出的方法用于分析一款为相位插值 CDR 提供高频时钟的 SBPLL, 拓扑结构同文献[2], 采用  $0.13~\mu m$  CMOS 工艺。图 3(a)中各关键晶体管尺寸为: M1 为  $12.0~\mu/300~n$ , M2 为  $3.0~\mu/300~n$ , M3 为  $16.2~\mu/300~n$ , M4 为  $5.2~\mu/300~n$ , M5 为  $5.2~\mu/300~n$ 。SBPLL 的动态参数如表  $1~\mu m$ 示。

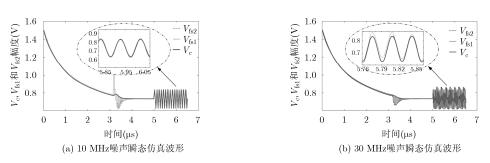

首先用瞬态仿真评估 SBPLL 的 SNR。在电源上加入振幅为 100 mV、不同频率的正弦噪声。以图 6 所示的 30 MHz 正弦噪声为例,可见输出频率同样反复波动,周期抖动可以用统计函数计算。瞬态仿真可以有效估测 SBPLL 抖动性能,但为了获得可靠的统计数据,需要仿真大量的时钟周期,因此耗费时间较长(可能长达数小时至数天)并且不能指出提升 SNR 的方法。接下来采用本文提出的基于噪声传递函数的方法预测 SBPLL 的抖动性能,两者对比如图 7(a)所示。

图 7(b)所示为调整器闭环带宽分别为 25 MHz 和 140 MHz 条件下的 SBPLL 瞬态仿真。当调整器闭环带宽增加时,周期抖动下降,验证了本文方法。本文方法可以在功率谱密度已知的条件下预测 PLL的抖动性能,不局限于正弦噪声。

可见在此例中瞬态仿真预测的周期性抖动和本 文提出的方法得到的结果除了最大值之外相互吻 合,瞬态仿真预测的周期抖动最大值高于本文方法,

表 1 SBPLL 动态参数

| 参数                    | 含义         | 数值                 |

|-----------------------|------------|--------------------|

| ζ                     | 阻尼系数       | 1.3                |

| $\omega_{\mathrm{n}}$ | 噪声角频率      | $1.4~\mathrm{MHz}$ |

| $A_0$                 | NMOS 本征增益  | 32                 |

| $A_{\rm a}$           | OTA 直流增益   | 35                 |

| $T_0$                 | PLL 输出时钟周期 | $1 \mathrm{\ ns}$  |

| $T_{ m ref}$          | PLL 参考时钟周期 | 40  ns             |

| N                     | PLL 分频比    | 40                 |

图 7 仿真结果对比

图 8  $V_{\rm c}$  ,  $V_{\rm fs1}$  和  $V_{\rm fs2}$  的瞬态仿真波形

原因解释如下。第 2 节假设 $V_c$ , $V_{\rm fal}$ 和 $V_{\rm fa2}$ 在 SBPLL 锁定时相等,但在 SBPLL 由于电源噪声而偏离锁定状态时这一点就不能成立了。图 8(a)和图 8(b)分别为 $V_c$ , $V_{\rm fal}$ 和 $V_{\rm fa2}$ 在输入 10 MHz 和 30 MHz 噪声下的瞬态波形,可见 3 个电压相等的假设在前者还成立,而后者就不再成立。同时,一些其他方面的原因,如电荷泵 UP、DN 电流不匹配以及从时钟缓冲器和分频器耦合的噪声等等,会恶化抖动性能。这一切可以在瞬态仿真中体现,却没有包含在本文的方法之中。

(a)瞬态仿真与本文方法结果对比

尽管瞬态仿真和本文方法之间存在误差,但采 用本文方法寻找使 SBPLL 抖动性能最差的电源噪 声频率范围却是有意义的。而后便可以采用各种方 法减少该频率区域的电源噪声。

#### 4 总结

本文提出了一种预测 SBPLL 在电源噪声下的

抖动性能的方法,详细分析了 SBPLL 中的复制偏置 图调整器在电源噪声抑制中的作用。分析表明需要 在调整器带宽和和 SNR 之间做权衡,同时应当将调 整器输入端的寄生电容最小化。瞬态仿真结果和本 文方法的对比表明本文方法可以有效预测抖动性 能,并且具有耗时短,以及可以为提高 SBPLL 抖动 性能提供参考的优势。

(b)两种不同调整器带宽下的瞬态仿真结果

# 参考文献

- [1] MANEATIS J G. Low-jitter process-independent DLL and PLL based on self-biased techniques[J]. *IEEE Journal of Solid-State Circuits*, 1996, 31(11): 1723–1732. doi: 10.1109/ JSSC.1996.542317.

- [2] MANEATIS J G, KIM J, MCCLATCHIE I, et al. Self-biased high-bandwidth low-jitter 1-to-4096 multiplier clock generator PLL[J]. IEEE Journal of Solid-State Circuits, 2003, 38(11): 1795–1803. doi: 10.1109/JSSC.2003.818298.

- [3] GANG Yan, CHENXIAO Ren, ZHENDONG Guo, et al. A self-biased PLL with current-mode filter for clock generation[C]. ISSCC 2005 IEEE International Digest of Technical Papers Solid-State Circuits Conference, San Francisco, CA, USA, 2005: 420–421 Vol. 421.

- [4] GHOSH P P, and XIAO E. A 2.5 GHz radiation hard fully self-biased PLL using 0.25 um SOS-CMOS technology[C]. 2009 IEEE International Conference on IC Design and Technology, Austin, TX, USA, 2009: 121–124.

- [5] VISWANATHAN B, VISWAM V, Vettickatt J J, et al. 4 GHz 130 nm low voltage PLL based on self biased technique[C]. The 23rd International Conference on VLSI Design, Bangalore, India, 2010: 330–334.

- [6] YOGESH M, DIETL M, SAREEN P, et al. A low power, self-biased, bandwidth tracking semi-digital PLL design[C]. 2012 IEEE International Conference on Electronics Design, Systems and Applications (ICEDSA), Kuala Lumpur, Malaysia, 2012: 135–140.

- [7] GAO X, KLUMPERINK E A M, GERAEDTS P F J, et al. Jitter analysis and a benchmarking figure-of-merit for phase-locked loops[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2009, 56(2): 117–121. doi: 10.1109 /TCSII.2008.2010189.

- [8] ZHAO B, and YANG H. Supply-noise interactions among submodules inside a charge-pump PLL[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2015, 23(4): 771–775. doi: 10.1109/TVLSI.2014. 2317710.

- [9] BIDAJ K, BEGUERET J B, HOUDALI N, et al. Time-domain PLL modeling and RJ/DJ jitter decomposition[C]. 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, Canada, 2016: 185–188.

- [10] BONDALAPATI P, and NAMGOONG W. Nonlinear analysis of bang-bang digital PLL with accumulative noise using Markov chains[C]. 2016 Texas Symposium on Wireless and Microwave Circuits and Systems (WMCS), Waco, TX, USA, 2016: 1-4.

- [11] VASILYEV G S, KUZICHKIN O R, KURILOV I A, et al. Analysis of noise properties of hybrid frequency synthesizer with autocompensating phase noise of DDS and PLL[C]. 2016

- International Siberian Conference on Control and Communications (SIBCON), Shell, Singapore, 2016: 1–6.

- [12] ARAKALI A, GONDI S, and HANUMOLU P K. Low-power supply-regulation techniques for ring oscillators in phase-locked loops using a split-tuned architecture [J]. IEEE Journal of Solid-State Circuits, 2009, 44(8): 2169–2181. doi: 10.1109/JSSC.2009.2022916.

- [13] ZHU K, SAXENA V, WU X, et al. Design analysis of a 12.5 GHz PLL in 130 nm SiGe BiCMOS process[C]. 2015 IEEE Workshop on Microelectronics and Electron Devices (WMED), Boise, ID, USA, 2015: 1–4.

- [14] LIU L and POKHAREL R. Compact modeling of phase-locked loop frequency synthesizer for transient phase noise and jitter simulation[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2016, 35(1): 166–170. doi: 10.1109/TCAD.2015.2472018.

- [15] GARDNER F. Charge-pump phase-lock loops[J]. IEEE Transactions on Communications, 1980, 28(11): 1849–1858. doi: 10.1109/TCOM.1980.1094619.

- [16] CASPER B and O'MAHONY F. Clocking analysis, implementation and measurement techniques for high-speed data links—a tutorial[J]. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2009, 56(1): 17–39. doi: 10.1109/ TCSI.2008.931647.

- 李天一: 男,1990年生,博士生,研究方向为高速串行接口时钟数据恢复电路.

- 许晓冬: 男,1985年生,博士,研究方向为射频电路设计、锁相 环设计.

- 尹 韬: 男,1981 年生,博士,副研究员,研究方向为模拟/混合信号集成电路设计、MEMS 传感器高性能接口芯片设计

- 韦援丰: 男,1983年生,博士,助理研究员,研究方向为高速 IO、 PLL 芯片设计.

- 黄国城: 男,1989 年生,博士,研究方向为模拟/混合信号集成 电路设计.

- 李 威: 女,1983年生,博士,助理研究员,研究方向为大规模 现场可编程逻辑阵列设计.

- 杨海钢: 男,1960年生,博士,研究员,研究方向为微电子学与 集成电路技术、可编程信号处理器架构与 SoC 设计.